еҲ©з”ЁPGзҪ‘иЎЁд»ҝзңҹжҠҖжңҜеҸҜд»Ҙжҳҫи‘—жҸҗеҚҮз”өи·Ҝд»ҝзңҹзҡ„ж•ҲзҺҮпјҢеҮҸе°‘д»ҝзңҹж—¶й—ҙпјҢеўһејәи®ҫи®Ўзҡ„еҮҶзЎ®жҖ§гҖӮйҖҡиҝҮдјҳеҢ–зҪ‘иЎЁз»“жһ„гҖҒйҮҮз”ЁеҲҶеұӮд»ҝзңҹзӯ–з•Ҙд»ҘеҸҠз»“еҗҲ硬件еҠ йҖҹжүӢж®өпјҢе·ҘзЁӢеёҲиғҪеӨҹжӣҙеҝ«йҖҹең°йӘҢиҜҒз”өи·Ҝи®ҫи®ЎпјҢзј©зҹӯејҖеҸ‘е‘ЁжңҹгҖӮжң¬ж–Үе°ҶиҜҰз»Ҷд»Ӣз»ҚеҰӮдҪ•еҲ©з”ЁPGзҪ‘иЎЁд»ҝзңҹжҠҖжңҜжҸҗеҚҮз”өи·Ҝд»ҝзңҹж•ҲзҺҮпјҢ并结еҗҲе®һйҷ…жЎҲдҫӢеҲҶжһҗ pg电子手机网址е…·дҪ“ж“ҚдҪңж–№жі•е’Ңж•ҲжһңжҸҗеҚҮж–№жЎҲпјҢеё®еҠ©и®ҫи®Ўдәәе‘ҳе®һзҺ°й«ҳж•ҲгҖҒзІҫеҮҶзҡ„з”өи·Ҝд»ҝзңҹзӣ®ж ҮгҖӮ

дјҳеҢ–PGзҪ‘иЎЁз»“жһ„д»ҘжҸҗеҚҮд»ҝзңҹж•ҲзҺҮ

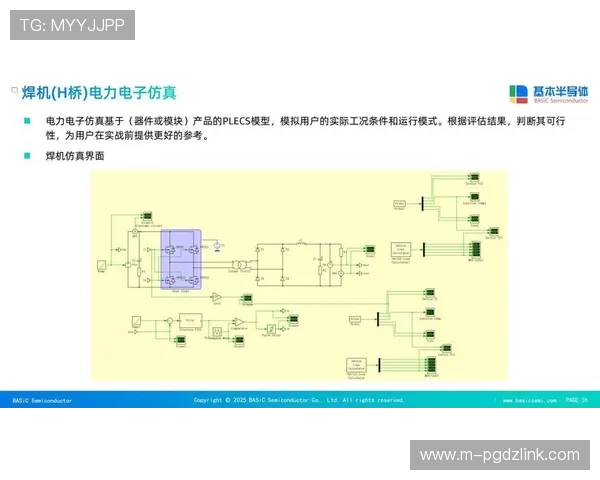

еҗҲзҗҶеҲ’еҲҶзҪ‘иЎЁеұӮзә§з»“жһ„

еңЁз”өи·Ҝд»ҝзңҹдёӯпјҢеҗҲзҗҶеҲ’еҲҶPGзҪ‘иЎЁзҡ„еұӮзә§з»“жһ„жҳҜжҸҗеҚҮд»ҝзңҹж•ҲзҺҮзҡ„е…ій”®гҖӮйҖҡиҝҮе°ҶеӨҚжқӮз”өи·ҜжӢҶеҲҶжҲҗеӨҡдёӘеӯҗзҪ‘иЎЁпјҢе·ҘзЁӢеёҲеҸҜд»ҘеңЁдёҚеҗҢеұӮзә§д№Ӣй—ҙиҝӣиЎҢеұҖйғЁд»ҝзңҹпјҢеҮҸе°‘ж•ҙдҪ“д»ҝзңҹиҙҹжӢ…гҖӮйҮҮз”ЁеҲҶеұӮи®ҫи®ЎдёҚд»…еҸҜд»Ҙзј©зҹӯд»ҝзңҹж—¶й—ҙпјҢиҝҳиғҪж–№дҫҝе®ҡдҪҚз”өи·Ҝдёӯзҡ„жҪңеңЁй—®йўҳгҖӮжҜ”еҰӮпјҢе°ҶжЁЎжӢҹйғЁеҲҶе’Ңж•°еӯ—йғЁеҲҶеҲҶејҖеӨ„зҗҶпјҢйҒҝе…ҚдёҚеҝ…иҰҒзҡ„д»ҝзңҹи®Ўз®—пјҢжҸҗй«ҳж•ҙдҪ“ж•ҲзҺҮгҖӮ

з®ҖеҢ–зҪ‘иЎЁдёӯзҡ„еҶ—дҪҷдҝЎжҒҜ

еңЁз”ҹжҲҗPGзҪ‘иЎЁж—¶пјҢеҺ»йҷӨеҶ—дҪҷдҝЎжҒҜд№ҹжҳҜжҸҗеҚҮд»ҝзңҹйҖҹеәҰзҡ„йҮҚиҰҒжүӢж®өгҖӮйҖҡиҝҮдјҳеҢ–зҪ‘иЎЁз”ҹжҲҗе·Ҙе…·пјҢеҮҸе°‘дёҚеҝ…иҰҒзҡ„иҝһжҺҘе’Ңе…ғ件жҸҸиҝ°пјҢеҸҜд»ҘйҷҚдҪҺд»ҝзңҹжЁЎеһӢзҡ„еӨҚжқӮеәҰгҖӮиҝҷж ·дёҚд»…еҮҸе°‘дәҶд»ҝзңҹжүҖйңҖзҡ„и®Ўз®—иө„жәҗпјҢиҝҳиғҪйҒҝе…Қеӣ еҶ—дҪҷдҝЎжҒҜеј•иө·зҡ„д»ҝзңҹиҜҜе·®гҖӮеҗҲзҗҶзҡ„з®ҖеҢ–зӯ–з•Ҙеә”еңЁдҝқиҜҒд»ҝзңҹзІҫеәҰзҡ„еүҚжҸҗдёӢпјҢжңҖеӨ§зЁӢеәҰең°еҮҸе°‘зҪ‘иЎЁзҡ„еӨҚжқӮеәҰпјҢд»ҺиҖҢжҸҗеҚҮд»ҝзңҹж•ҲзҺҮгҖӮ

йҮҮз”ЁеҲҶеұӮд»ҝзңҹзӯ–з•Ҙе®һзҺ°еҝ«йҖҹйӘҢиҜҒ

йҖҗеұӮд»ҝзңҹдёҺйӘҢиҜҒ

еҲҶеұӮд»ҝзңҹзӯ–з•ҘжҳҜжҸҗеҚҮз”өи·Ҝд»ҝзңҹж•ҲзҺҮзҡ„йҮҚиҰҒжүӢж®өгҖӮе·ҘзЁӢеёҲеҸҜд»Ҙе…ҲеҜ№з”өи·Ҝзҡ„й«ҳеұӮж¬ЎжЁЎеһӢиҝӣиЎҢеҝ«йҖҹйӘҢиҜҒпјҢзЎ®и®Өж•ҙдҪ“еҠҹиғҪжӯЈзЎ®жҖ§еҗҺпјҢеҶҚйҖҗжӯҘж·ұе…ҘеҲ°еӯҗжЁЎеқ—зҡ„иҜҰз»Ҷд»ҝзңҹгҖӮиҝҷз§ҚйҖҗеұӮйӘҢиҜҒзҡ„ж–№жі•еҸҜд»ҘеңЁж—©жңҹеҸ‘зҺ°и®ҫи®Ўзјәйҷ·пјҢйҒҝе…ҚеңЁеӨҚжқӮжЁЎеһӢдёҠжөӘиҙ№еӨ§йҮҸж—¶й—ҙгҖӮеҲ©з”ЁPGзҪ‘иЎЁзҡ„еҲҶеұӮзү№жҖ§пјҢйҖҗжӯҘзј©е°Ҹд»ҝзңҹиҢғеӣҙпјҢжһҒеӨ§жҸҗй«ҳйӘҢиҜҒж•ҲзҺҮгҖӮ

з»“еҗҲ硬件еҠ йҖҹжҠҖжңҜ

硬件еҠ йҖҹжҠҖжңҜеҰӮFPGAгҖҒGPUзӯүзҡ„еј•е…ҘпјҢдёәPGзҪ‘иЎЁд»ҝзңҹжҸҗдҫӣдәҶејәеӨ§ж”ҜжҢҒгҖӮйҖҡиҝҮе°ҶйғЁеҲҶд»ҝзңҹд»»еҠЎиҪ¬з§»еҲ°зЎ¬д»¶е№іеҸ°дёҠпјҢеҸҜд»Ҙе®һзҺ°е№¶иЎҢеӨ„зҗҶпјҢеӨ§е№…еәҰзј©зҹӯд»ҝзңҹж—¶й—ҙгҖӮдҫӢеҰӮпјҢеҲ©з”ЁGPUзҡ„并иЎҢи®Ўз®—иғҪеҠӣпјҢеҸҜд»ҘеҗҢж—¶еӨ„зҗҶеӨҡдёӘеӯҗзҪ‘иЎЁзҡ„д»ҝзңҹд»»еҠЎпјҢжҳҫи‘—жҸҗеҚҮж•ҙдҪ“д»ҝзңҹйҖҹеәҰгҖӮз»“еҗҲ硬件еҠ йҖҹзҡ„еҲҶеұӮд»ҝзңҹзӯ–з•ҘпјҢиғҪеӨҹеңЁдҝқиҜҒд»ҝзңҹзІҫеәҰзҡ„еҗҢж—¶пјҢжһҒеӨ§ең°жҸҗй«ҳд»ҝзңҹж•ҲзҺҮпјҢж»Ўи¶іеҝ«йҖҹйӘҢиҜҒзҡ„йңҖжұӮгҖӮ

е®һйҷ…жЎҲдҫӢеҲҶжһҗпјҡPGзҪ‘иЎЁд»ҝзңҹжҠҖжңҜеңЁиҠҜзүҮи®ҫи®Ўдёӯзҡ„еә”з”Ё

жЎҲдҫӢиғҢжҷҜдёҺйңҖжұӮ

жҹҗеҚҠеҜјдҪ“е…¬еҸёеңЁиҠҜзүҮи®ҫи®ЎиҝҮзЁӢдёӯпјҢйқўдёҙеӨҚжқӮз”өи·Ҝзҡ„д»ҝзңҹж—¶й—ҙиҝҮй•ҝй—®йўҳгҖӮдј з»ҹд»ҝзңҹж–№жі•иҖ—иҙ№еӨ§йҮҸж—¶й—ҙпјҢеҪұе“ҚдәҶи®ҫи®ЎиҝӣеәҰгҖӮдёәжӯӨпјҢеӣўйҳҹеҶіе®ҡеј•е…ҘPGзҪ‘иЎЁд»ҝзңҹжҠҖжңҜпјҢйҖҡиҝҮдјҳеҢ–зҪ‘иЎЁз»“жһ„е’ҢйҮҮз”ЁеҲҶеұӮд»ҝзңҹзӯ–з•ҘпјҢжҸҗеҚҮд»ҝзңҹж•ҲзҺҮгҖӮзӣ®ж ҮжҳҜе®һзҺ°еҝ«йҖҹйӘҢиҜҒз”өи·ҜеҠҹиғҪпјҢзЎ®дҝқи®ҫи®ЎиҙЁйҮҸпјҢеҗҢж—¶зј©зҹӯејҖеҸ‘е‘ЁжңҹгҖӮ

е®һж–Ҫж–№жЎҲдёҺж•Ҳжһң

еӣўйҳҹйҰ–е…ҲеҜ№з”өи·ҜиҝӣиЎҢеҗҲзҗҶеҲ’еҲҶпјҢе°ҶPGзҪ‘иЎЁеҲҶеұӮеӨ„зҗҶпјҢеҮҸе°‘еҶ—дҪҷдҝЎжҒҜпјҢдјҳеҢ–жЁЎеһӢз»“жһ„гҖӮйҡҸеҗҺпјҢз»“еҗҲGPU硬件еҠ йҖҹжҠҖжңҜпјҢе®һзҺ°еӨҡеұӮж¬Ўд»ҝзңҹ并иЎҢеӨ„зҗҶгҖӮз»ҸиҝҮдёҖж®өж—¶й—ҙзҡ„и°ғиҜ•пјҢд»ҝзңҹж—¶й—ҙд»ҺеҺҹжқҘзҡ„ж•°е°Ҹж—¶зј©зҹӯеҲ°дёҚеҲ°дёҖе°Ҹж—¶пјҢйӘҢиҜҒж•ҲзҺҮеӨ§е№…жҸҗеҚҮгҖӮжңҖз»ҲпјҢи®ҫи®ЎеӣўйҳҹеңЁдҝқиҜҒз”өи·ҜжҖ§иғҪзҡ„еүҚжҸҗдёӢпјҢжҸҗеүҚе®ҢжҲҗдәҶйӘҢиҜҒд»»еҠЎпјҢдёәеҗҺз»ӯзҡ„еҲ¶йҖ жөҒзЁӢжҸҗдҫӣдәҶжңүеҠӣдҝқйҡңгҖӮиҝҷдёҖжЎҲдҫӢе……еҲҶдҪ“зҺ°дәҶеҲ©з”ЁPGзҪ‘иЎЁд»ҝзңҹжҠҖжңҜжҸҗеҚҮз”өи·Ҝд»ҝзңҹж•ҲзҺҮзҡ„е®һйҷ…ж•ҲжһңгҖӮ

з»јдёҠжүҖиҝ°пјҢеҲ©з”ЁPGзҪ‘иЎЁд»ҝзңҹжҠҖжңҜжҸҗеҚҮз”өи·Ҝд»ҝзңҹж•ҲзҺҮпјҢж—ўйңҖиҰҒдјҳеҢ–зҪ‘иЎЁз»“жһ„пјҢеҸҲиҰҒйҮҮз”ЁеҲҶеұӮд»ҝзңҹзӯ–з•Ҙе’Ң硬件еҠ йҖҹжүӢж®өгҖӮйҖҡиҝҮеҗҲзҗҶзҡ„и®ҫи®Ўе’ҢжҠҖжңҜеә”з”ЁпјҢе·ҘзЁӢеёҲеҸҜд»Ҙжҳҫи‘—зј©зҹӯд»ҝзңҹж—¶й—ҙпјҢжҸҗй«ҳйӘҢиҜҒзҡ„еҮҶзЎ®жҖ§пјҢдёәз”өи·Ҝи®ҫи®Ўзҡ„еҝ«йҖҹиҝӯд»ЈжҸҗдҫӣжңүеҠӣж”ҜжҢҒгҖӮжңӘжқҘпјҢйҡҸзқҖд»ҝзңҹжҠҖжңҜзҡ„дёҚж–ӯеҸ‘еұ•пјҢPGзҪ‘иЎЁд»ҝзңҹе°ҶеңЁз”өи·Ҝи®ҫи®Ўдёӯжү®жј”и¶ҠжқҘи¶ҠйҮҚиҰҒзҡ„и§’иүІпјҢеҠ©еҠӣиЎҢдёҡиҝҲеҗ‘жӣҙй«ҳзҡ„ж•ҲзҺҮе’Ңжӣҙдјҳзҡ„жҖ§иғҪгҖӮ